- 您现在的位置:买卖IC网 > Sheet目录3753 > ATMEGA169P-16MCHR (Atmel)MCU AVR 16KB FLASH 16MHZ 64-VQFN

2005 Microchip Technology Inc.

Preliminary

DS41265A-page 199

PIC16F946

ADCON0

1Fh

0000 0000

uuuu uuuu

OPTION_REG

81h/181h

1111 1111

uuuu uuuu

TRISA

85h

1111 1111

uuuu uuuu

TRISB

86h/186h

1111 1111

uuuu uuuu

TRISC

87h

1111 1111

uuuu uuuu

TRISD

88h

1111 1111

uuuu uuuu

TRISE

89h

1111 1111

uuuu uuuu

PIE1

8Ch

0000 0000

uuuu uuuu

PIE2

8Dh

0000 0000

uuuu uuuu

PCON

8Eh

--01 --0x

--0u --uu

(1,5)

--uu --uu

OSCCON

8Fh

-110 q000

-110 x000

-uuu uuuu

OSCTUNE

90h

---0 0000

---u uuuu

ANSEL

91h

1111 1111

uuuu uuuu

PR2

92h

1111 1111

SSPADD

93h

0000 0000

uuuu uuuu

SSPSTAT

94h

0000 0000

uuuu uuuu

WPUB

95h

1111 1111

uuuu uuuu

IOCB

96h

0000 ----

uuuu ----

CMCON1

97h

---- --10

---- --uu

TXSTA

98h

0000 -010

uuuu -uuu

SPBRG

99h

0000 0000

uuuu uuuu

CMCON0

9Ch

0000 0000

uuuu uuuu

VRCON

9Dh

0-0- 0000

u-u- uuuu

ADRESL

9Eh

xxxx xxxx

uuuu uuuu

ADCON1

9Fh

-000 ----

-uuu ----

WDTCON

105h

---0 1000

---u uuuu

LCDCON

107h

0001 0011

uuuu uuuu

LCDPS

108h

0000 0000

uuuu uuuu

LVDCON

109h

--00 -100

--uu -uuu

EEDATL

10Ch

0000 0000

uuuu uuuu

EEADRL

10Dh

0000 0000

uuuu uuuu

EEDATH

10Eh

--00 0000

0000 0000

uuuu uuuu

EEADRH

10Fh

---0 0000

0000 0000

uuuu uuuu

LCDDATA0

110h

xxxx xxxx

uuuu uuuu

LCDDATA1

111h

xxxx xxxx

uuuu uuuu

LCDDATA2

112h

xxxx xxxx

uuuu uuuu

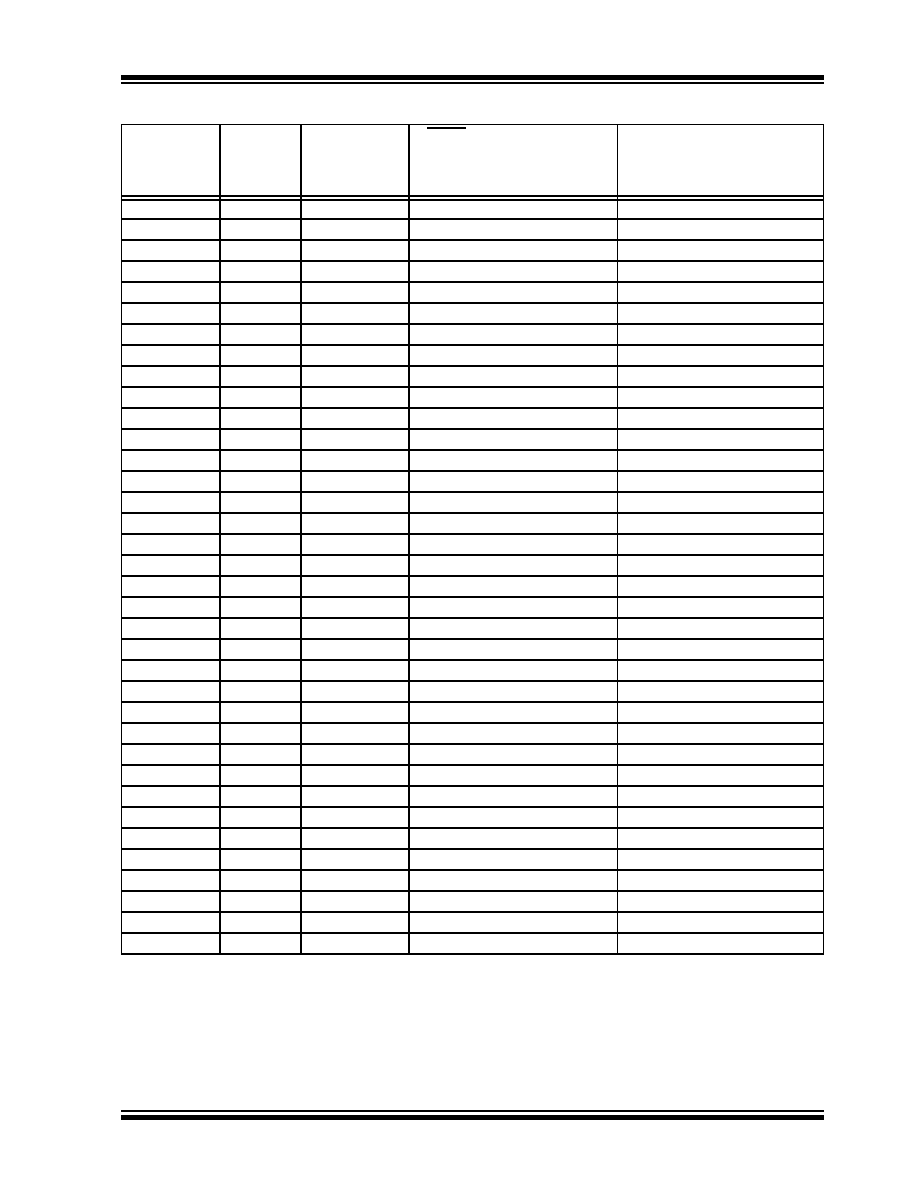

TABLE 16-4:

INITIALIZATION CONDITION FOR REGISTERS (CONTINUED)

Register

Address

Power-on

Reset

MCLR Reset

WDT Reset

Brown-out Reset(1)

Wake-up from Sleep

through interrupt

Wake-up from Sleep

through WDT time-out

Legend: u = unchanged, x = unknown, – = unimplemented bit, reads as ‘0’, q = value depends on condition.

Note 1:

If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2:

One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

3:

When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt

vector (0004h).

4:

See Table 16-5 for Reset value for specific condition.

5:

If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

2-1546217-0

TERM BLK RCPT 20POS SIDE 5.08MM

1-1546217-9

TERM BLK RCPT 19POS SIDE 5.08MM

1-1546217-8

TERM BLK RCPT 18POS SIDE 5.08MM

1-1546217-7

TERM BLK RCPT 17POS SIDE 5.08MM

1-1546217-6

TERM BLK RCPT 16POS SIDE 5.08MM

1-1546217-5

TERM BLK RCPT 15POS SIDE 5.08MM

1-1546217-4

TERM BLK RCPT 14POS SIDE 5.08MM

1-1546217-3

TERM BLK RCPT 13POS SIDE 5.08MM

相关代理商/技术参数

ATMEGA169P-16MCU

功能描述:8位微控制器 -MCU AVR 16KB, 512B EE 16MHz 1KB SRAM, 5V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-16MU

功能描述:8位微控制器 -MCU AVR 16K FLASH 512B EE 1K SRAM LCD ADC RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-16MU SL383

制造商:Atmel Corporation 功能描述:MCU 8BIT ATMEGA RISC 16KB FLASH 3.3V/5V 64PIN MLF - Tape and Reel

ATMEGA169P-16MUR

功能描述:8位微控制器 -MCU AVR LCD 16KB FLSH EE 512B 1KB SRAM-16MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA169P-8AU

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169P-8MU

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169PA

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller with 16K Bytes In-System Programmable Flash

ATMEGA169PA_1

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:High Endurance Non-volatile Memory segments